Yarı iletken sanayisinde çip üretiminin en şiddetli evrelerinden biri olan katman hizalamasında devrim niteliğinde bir gelişme yaşanıyor. Massachusetts Amherst Üniversitesi’nden bilim insanları, lazerler ve metalensler kullanarak atomik hassasiyette hizalama sağlayabilen yeni bir formül geliştirdiklerini duyurdu. SciTechDaily tarafından aktarılan bu yenilik, bilhassa 3D çip dizaynlarında ve çoklu yonga (chiplet) entegrasyonlarında oyun değiştirici bir rol oynayabilir.

Yarı iletken sanayisinde çip üretiminin en şiddetli evrelerinden biri olan katman hizalamasında devrim niteliğinde bir gelişme yaşanıyor. Massachusetts Amherst Üniversitesi’nden bilim insanları, lazerler ve metalensler kullanarak atomik hassasiyette hizalama sağlayabilen yeni bir formül geliştirdiklerini duyurdu. SciTechDaily tarafından aktarılan bu yenilik, bilhassa 3D çip dizaynlarında ve çoklu yonga (chiplet) entegrasyonlarında oyun değiştirici bir rol oynayabilir. Modern çip üretimi, her biri çok sayıda üretim adımı içeren karmaşık bir süreçtir. Bilhassa mantık devreleri içeren wafer’larda, yaklaşık 4.000 farklı üretim basamağı çeşitli makineler tarafından gerçekleştirilir. Bu süreçte, bir katmanın alttakiyle harika halde hizalanması — yani overlay accuracy — en kritik hususlardan biridir.

Mevcut teknolojiler bu hizalamayı optik ölçüm sistemleri, hizalama işaretleri ve kapalı döngü denetim düzenekleriyle sağlar. Fakat bu sistemlerin yaklaşık 2 – 2,5 nanometrelik bir çözünürlük sınırı ve farklı derinliklerdeki katmanlara tıpkı anda odaklanamamak üzere önemli kısıtlamaları bulunuyor. Bu da bilhassa dikey istifli (stacked) çip dizaynlarında sorun yaratabiliyor.

Metalens ve lazerle gelen devrim

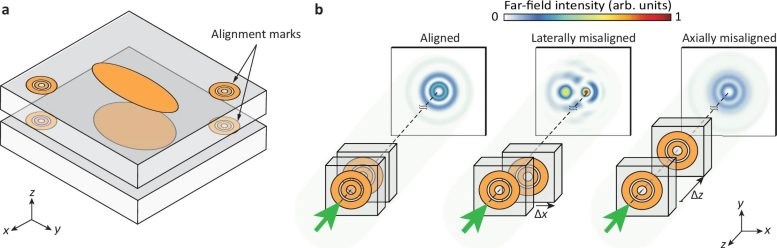

UMass Amherst araştırmacılarının önerdiği usul, özel olarak tasarlanmış eşmerkezli metalenslerin çip yüzeyine yerleştirilmesini içeriyor. Bu lensler bir lazer ışınıyla aydınlatıldığında holografik teşebbüs desenleri oluşturuyor. Oluşan desenler, çip katmanları ortasındaki sapmanın istikametini ve ölçüsünü üç boyutta da ortaya koyabiliyor.

UMass Amherst araştırmacılarının önerdiği usul, özel olarak tasarlanmış eşmerkezli metalenslerin çip yüzeyine yerleştirilmesini içeriyor. Bu lensler bir lazer ışınıyla aydınlatıldığında holografik teşebbüs desenleri oluşturuyor. Oluşan desenler, çip katmanları ortasındaki sapmanın istikametini ve ölçüsünü üç boyutta da ortaya koyabiliyor. En dikkat cazip bulgu ise bu sistemin yatayda sadece 0.017 nanometre, dikeyde ise 0.134 nanometre üzere harikulâde düşük sapmaları algılayabilmesi. Bu, sırf bilim insanlarının orjinal maksatları olan 100 nanometre hassasiyetini aşmakla kalmıyor, tıpkı vakitte günümüz optik mikroskoplarının çözünürlük hudutlarını da geride bırakıyor. Ayrıyeten, sistemin çip üretimi ve 3D çip entegrasyonundaki en karmaşık adımlardan birini kolaylaştırarak üretim maliyetlerini düşürebileceğine inanıyorlar.

Ancak her teknolojik atılımda olduğu üzere, bu yolun de önünde kimi mahzurlar var. Sistemin mevcut litografi, bağlama ve TSV (Through-Silicon Via) üzere üretim araçlarıyla entegre edilip edilemeyeceği hâlâ net değil. Şayet entegrasyon mümkün olmazsa, bu çığır açıcı teknolojinin yarı iletken üretiminde yaygınlaşması sıkıntı olabilir.